Hardware and Energy-Efficient Stochastic LU Decomposition Scheme for MIMO Receivers

•Download as DOCX, PDF•

0 likes•89 views

Hardware and Energy-Efficient Stochastic LU Decomposition Scheme for MIMO Receivers

Report

Share

Report

Share

Recommended

Input-Based Dynamic Reconfiguration of Approximate Arithmetic Units for Video...

Input-Based Dynamic Reconfiguration of Approximate Arithmetic Units for Video...Pvrtechnologies Nellore

Recommended

Input-Based Dynamic Reconfiguration of Approximate Arithmetic Units for Video...

Input-Based Dynamic Reconfiguration of Approximate Arithmetic Units for Video...Pvrtechnologies Nellore

Quality of-protection-driven data forwarding for intermittently connected wir...

Quality of-protection-driven data forwarding for intermittently connected wir...Pvrtechnologies Nellore

Control cloud-data-access-privilege-and-anonymity-with-fully-anonymous-attrib...

Control cloud-data-access-privilege-and-anonymity-with-fully-anonymous-attrib...Pvrtechnologies Nellore

Control cloud data access privilege and anonymity with fully anonymous attrib...

Control cloud data access privilege and anonymity with fully anonymous attrib...Pvrtechnologies Nellore

Closeness through-microaggregation-strict-privacy-with-enhanced-utility-prese...

Closeness through-microaggregation-strict-privacy-with-enhanced-utility-prese...Pvrtechnologies Nellore

A distortion-resistant-routing-framework-for-video-traffic-in-wireless-multih...

A distortion-resistant-routing-framework-for-video-traffic-in-wireless-multih...Pvrtechnologies Nellore

A secure and dynamic multi keyword ranked search scheme over encrypted cloud ...

A secure and dynamic multi keyword ranked search scheme over encrypted cloud ...Pvrtechnologies Nellore

More Related Content

More from Pvrtechnologies Nellore

Quality of-protection-driven data forwarding for intermittently connected wir...

Quality of-protection-driven data forwarding for intermittently connected wir...Pvrtechnologies Nellore

Control cloud-data-access-privilege-and-anonymity-with-fully-anonymous-attrib...

Control cloud-data-access-privilege-and-anonymity-with-fully-anonymous-attrib...Pvrtechnologies Nellore

Control cloud data access privilege and anonymity with fully anonymous attrib...

Control cloud data access privilege and anonymity with fully anonymous attrib...Pvrtechnologies Nellore

Closeness through-microaggregation-strict-privacy-with-enhanced-utility-prese...

Closeness through-microaggregation-strict-privacy-with-enhanced-utility-prese...Pvrtechnologies Nellore

A distortion-resistant-routing-framework-for-video-traffic-in-wireless-multih...

A distortion-resistant-routing-framework-for-video-traffic-in-wireless-multih...Pvrtechnologies Nellore

A secure and dynamic multi keyword ranked search scheme over encrypted cloud ...

A secure and dynamic multi keyword ranked search scheme over encrypted cloud ...Pvrtechnologies Nellore

More from Pvrtechnologies Nellore (20)

A High-Speed FPGA Implementation of an RSD-Based ECC Processor

A High-Speed FPGA Implementation of an RSD-Based ECC Processor

Pre encoded multipliers based on non-redundant radix-4 signed-digit encoding

Pre encoded multipliers based on non-redundant radix-4 signed-digit encoding

Quality of-protection-driven data forwarding for intermittently connected wir...

Quality of-protection-driven data forwarding for intermittently connected wir...

Control cloud-data-access-privilege-and-anonymity-with-fully-anonymous-attrib...

Control cloud-data-access-privilege-and-anonymity-with-fully-anonymous-attrib...

Control cloud data access privilege and anonymity with fully anonymous attrib...

Control cloud data access privilege and anonymity with fully anonymous attrib...

Circuit ciphertext policy attribute-based hybrid encryption with verifiable

Circuit ciphertext policy attribute-based hybrid encryption with verifiable

Closeness through-microaggregation-strict-privacy-with-enhanced-utility-prese...

Closeness through-microaggregation-strict-privacy-with-enhanced-utility-prese...

A secure-anti-collusion-data-sharing-scheme-for-dynamic-groups-in-the-cloud

A secure-anti-collusion-data-sharing-scheme-for-dynamic-groups-in-the-cloud

A proximity-aware-interest-clustered-p2 p-file-sharing-system-docx

A proximity-aware-interest-clustered-p2 p-file-sharing-system-docx

A computational-dynamic-trust-model-for-user-authorization-docx

A computational-dynamic-trust-model-for-user-authorization-docx

A distortion-resistant-routing-framework-for-video-traffic-in-wireless-multih...

A distortion-resistant-routing-framework-for-video-traffic-in-wireless-multih...

A secure and dynamic multi keyword ranked search scheme over encrypted cloud ...

A secure and dynamic multi keyword ranked search scheme over encrypted cloud ...

Recently uploaded

young call girls in Green Park🔝 9953056974 🔝 escort Service

young call girls in Green Park🔝 9953056974 🔝 escort Service9953056974 Low Rate Call Girls In Saket, Delhi NCR

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf9953056974 Low Rate Call Girls In Saket, Delhi NCR

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...9953056974 Low Rate Call Girls In Saket, Delhi NCR

Recently uploaded (20)

young call girls in Green Park🔝 9953056974 🔝 escort Service

young call girls in Green Park🔝 9953056974 🔝 escort Service

INFLUENCE OF NANOSILICA ON THE PROPERTIES OF CONCRETE

INFLUENCE OF NANOSILICA ON THE PROPERTIES OF CONCRETE

CCS355 Neural Network & Deep Learning Unit II Notes with Question bank .pdf

CCS355 Neural Network & Deep Learning Unit II Notes with Question bank .pdf

Biology for Computer Engineers Course Handout.pptx

Biology for Computer Engineers Course Handout.pptx

Study on Air-Water & Water-Water Heat Exchange in a Finned Tube Exchanger

Study on Air-Water & Water-Water Heat Exchange in a Finned Tube Exchanger

Decoding Kotlin - Your guide to solving the mysterious in Kotlin.pptx

Decoding Kotlin - Your guide to solving the mysterious in Kotlin.pptx

Instrumentation, measurement and control of bio process parameters ( Temperat...

Instrumentation, measurement and control of bio process parameters ( Temperat...

Heart Disease Prediction using machine learning.pptx

Heart Disease Prediction using machine learning.pptx

Gfe Mayur Vihar Call Girls Service WhatsApp -> 9999965857 Available 24x7 ^ De...

Gfe Mayur Vihar Call Girls Service WhatsApp -> 9999965857 Available 24x7 ^ De...

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf

Exploring_Network_Security_with_JA3_by_Rakesh Seal.pptx

Exploring_Network_Security_with_JA3_by_Rakesh Seal.pptx

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...

CCS355 Neural Network & Deep Learning UNIT III notes and Question bank .pdf

CCS355 Neural Network & Deep Learning UNIT III notes and Question bank .pdf

Hardware and Energy-Efficient Stochastic LU Decomposition Scheme for MIMO Receivers

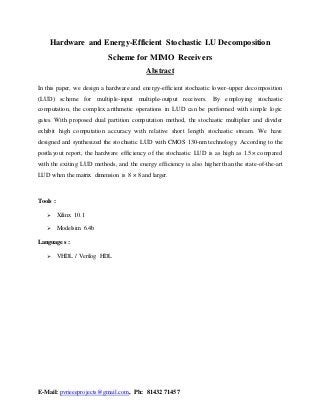

- 1. E-Mail: pvrieeeprojects@gmail.com, Ph: 81432 71457 Hardware and Energy-Efficient Stochastic LU Decomposition Scheme for MIMO Receivers Abstract In this paper, we design a hardware and energy-efficient stochastic lower–upper decomposition (LUD) scheme for multiple-input multiple-output receivers. By employing stochastic computation, the complex arithmetic operations in LUD can be performed with simple logic gates. With proposed dual partition computation method, the stochastic multiplier and divider exhibit high computation accuracy with relative short length stochastic stream. We have designed and synthesized the stochastic LUD with CMOS 130-nm technology. According to the postlayout report, the hardware efficiency of the stochastic LUD is as high as 1.5× compared with the exiting LUD methods, and the energy efficiency is also higher than the state-of-the-art LUD when the matrix dimension is 8 × 8 and larger. Tools : Xilinx 10.1 Modelsim 6.4b Languages : VHDL / Verilog HDL